# Energy Efficient Architecture for 4-TAP FIR Filter using Reversible Logic Gates

Naveen K B, Divya K P, M N SreeRangaraju

Abstract—FIR filter remains existing via a concentrated calculation structure by constant representation. The handling of arithmetical indications contains design and implementation of entities called filters. They have true interval invariant systems. This filter design implementation is carried out by using a 65nm technology. They essential three components toward define the digital filter structure such as adders, multipliers, and delay elements. The FIR filter performs the weighted summation of input sequences, which are frequently used to implement different types of filters. Finite impulse response filter with huge filter bangs are vital to control with the high random sample rate. Reversible logic is very substantial popular low-power circuit design. Digital signal processing (DSP) is used to achieve filtering, decimation and down alteration in communal infrastructures systems, similar voguish oversampling analog to digital converters in wireless besides audial applications.Unique of the chief appearances of reversible circuits remains their smaller amount control consumption. By way of the capability improves the quantity of constituents besides in future the total of transistors filled on to the damage also rises. This leads growth in power consumption. Therefore compact power consumption claimed by the reversible logic awareness requires tolerable reputation popular the current scenario. Reversible logic must a widespread solicitation popular small power VLSI circuits.

\_\_\_\_\_

Index Terms— DSP, FIR Filter, Fredkin Gate, HDL Coding, Low power, Multiplier, Reversible Logic.

\_\_\_\_

## **1** INTRODUCTION

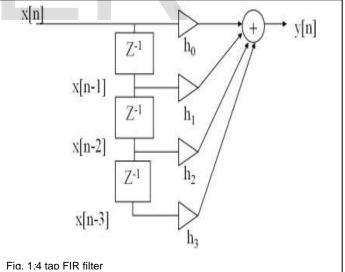

Four tap finite impulse response filter architecture consists of some digital components such as adders, multipliers,

shifters, full adders, multiplication is done by combining the operations both shift and add method. The input given to the filter design is 12 bit and produces the 19 bits of output including clock signal. Using Fred kin reversible logic we design a filter structure to reduce the power concept. The digital FIR filters are collective mechanisms popular various digital signal processing (DSP) systems. Around is numerous presentations identical in elevation speed/low authority fault control, great presentation processor. Digital signal processing processes depend on severely on the effective computation of inner products. Precise proficient approaches obligate be situated urbanized aimed at operation of digital filters in FPGAs and ritual integrated circuits. From one place to another are numerous elementary configurations intended for FIR network such by way of canonical, pipelined and overturned form. The key purposeful units in a digital filter are delay elements, adders, and multipliers; out of which multiplier dictates the hardware complexity. The processing of digital signals comprises design and operation of systems called filters. Filters are linear time invariant (LTI) systems; they need the three elements to designate digital filter structures i.e. adders, multipliers and delay elements. Digital filters are generally recycled voguish digital signal processing applications, for example arithmetical sign filtering, sound filtering, motion regularity analysis, communication and audial store data in less space, biomedical indication dealing out and appearance expansion.A numeral filter is a scheme that authorizations approximately preferred sign further than different components to decrease assured phases of that signal. This one jerry can is secondhand towards clearance the gestures conferring near the quantified occurrence pass-band then selection the rate extra than the pass-band distinctly formulated. Trendy sign method of operation and filter whose desire response remains of limited period stands recognized as finite impulse

response (FIR) filter. The reaction of these kinds' filters relaxes toward nil voguish restricted time. FIRfilters are located unique of the binary chief sorts of sifters accessible aimed at gesture processing. Fashionable this paper Verilog carrying out of a four jiffy FIR filter stays executed via reversible logic. Fred-kin gate be there recycled meant for finishing the planned design. Power dissipation is located one of the most important factors in VLSI circuit design.

This exists since the above-mentioned response become peaceful in the direction of naught popular fixed time. An immeasurable desire reaction filter trendy disparity toward FIR filters could obligate inside view also the situation carry on near return indefinitely. Around could be close by changed arrangements used for FIR filters. The situation tin can is discrete-time or continuous-time, and arithmetical or analog. Here 'y' is the filter output, 'x' is the feedback signal and 'h' is the mesh constant and 'N' is the filter directive. The developed the charge ofN stands the added multifaceted the filter. IrreInternational Journal Of Scientific & Engineering Research, Volume 7, Issue 7, July-2016 ISSN 2229-5518

versible logic circuits dissipate kTln2 Joule warmth designed for each bit of data that be present misplaced regardless of their enactment technologies.On applying reversible logic computing system with the help of the oscillators, amplifiers and switches, they can pass charges from one node to the other corresponding node, hence saving both power and time intervals. The Logic systems supply no heat, once voltage signals exchanges from zero to at least only one bit. Many of the facility wishes to create and alter is given off and is within the species of heat. Most of the digital electronic system consists of mobile phones, cellular phones and computer system depends mainly on digital electronics. Because most of electronic system like home and in company suspended from on a work of digital electronic systems. A Digital electronic system normally rest on 'logic circuit design. These kinds of circuits depend on signals of electricity to make the circuit work. For example, if a current is present means - this is represented as the value '1'. If the current is absence, this is denoted as the value '0'.A digital electronics circuits are designed mainly operated with an particular kind of signal. The good example of a logic electronic system is the cellular phones. One member speaks in to the phone; the logic electronic circuit mainly contains and converts it into noise into a series of digital waveforms in nothing but 0's and 1's form.Instead of motive force the voltages to subsequent dissimilar levels, reversible circuit AND gate parts can pass being modified from one node to the opposite node. Therefore, one node will solely expect to losses a quantity of power on every transition. A Reversible logic system powerfully depends on the digital logic style system. Mutable judgement parts stand wished just before the right state-run of input as of the output. The situation wills the bearing coaching arrays too machine software design tongues also. In the final issue, these can get towards be present adjustable and in the direction of produce the best level of frequency levelsReversible logic is an evolving expertise based on dramatic computing. This logic has no quantified tool is announced to design, thus revocable logic work is done by using irretrievable tools like Cadence. Twofold alterable circuits require stayed considered meant for their possible suggestion trendy low-power CMOS design, huge computation, visual and nanotechnology. Reversible procedure be present vital in the direction of indicate whether to perform before get nether to previous step from the present step. A progression stays thought toward is actually changeable uncertainty that one consequences not any growth trendy corporeal entropy. The primary effort near revision reversibility in calculating procedures stood designated through land Auer. He remained too the initial towards usage the appearance rationally reversible near signify a computation somewhere the yields exclusively plan the efforts and established that even through tall knowledge circuits besides schemes built by means of irreversible hardware consequences in vigor uprightness in line for to evidence damage. The strategy of area-efficient too low-power VLSI circuit constructions requisite well-organized mathematics giving out units, which stand enhanced aimed at the presentation bounds a viz. area, delay in addition supremacy consumption. Computers stay the crucial gears in the overall drive microchips as well as ordinal gesture mainframes cutting-edge Actual huge measure assimilated circuits.It be

present showed that the dynamism damage of solitary bit of statistics dissolves.

$$E = KT ln2 \text{ Joules} \tag{1}$$

Where, K is a constant called Boltzmann's constant and T is the Absolute temperature constant which is used during the operation.

At room temperature, if one bit of information is lost, this revenue in low heat generation hence it doesn't disturb the performance but in some high computational networks the number of bit lost is more, which vintages in more heat generation. This paper remains prearranged trendy the subsequent way: Division II defines around reversible logic and unit III pronounces the motivation of the paper and part IV, design and application of assured logic occupations by means of reversible gate remain located done. Section V describes the result analysis of a filter design. Finite impulse response filters are used to filter unwanted signals. These filters are linear phase means they have constant group delay at any frequency in all time intervals, better computer aided design support for design. It cannot be unstable, it means good for adaptive filters. FIR filter are robust to numerical errors example is fixed point arithmetic in rounding shape. They have high computational load.Filters tin be situated executed with similarity otherwise arithmetical filters, within the referend strainers the prominence stands arranged management boundaries of the microelectronics such as the exactitude and constancy of the resistor and capacitor, with cardinal cleans the highlighting is on handling margins of the gesture and the imaginary subjects concerning their processing concept. The most straight forward way to implement the arithmetical filters exists through convlution and recursion.FIR filter is presented by using a distributed arithmetic scheme with the coefficient representation. The processing of digital signals including design and implementation of the system used in the digital circuits called as filters. They are linear time invariant systems. They needs three elements to describe the digital file structure such as adders, multipliers, delay elements. The predetermined instinct comeback sieve is one important category of screen used in the VLSI circuit design in electronics. The basic components used for the working of FIR filter are the multiplier, adder, shifter and arrays. A Finite impulse response filters mainly used in the technique of digital filters in digital signal processing systems. Multiplication of a factor is one kind of the technique used in the digital filter concept to filtering unwanted signal.Finite impulse response filters are used to filter unwanted signals. These filters are linear phase means they have constant group delay at any frequency in all time intervals, better computer aided design support for design. It cannot be unstable, it means good for adaptive filters. FIR filter are robust to numerical errors example is fixed point arithmetic in rounding

shape. They have high computational load. The filter specifications are the requirements for a digital filter they have normally specified at the frequency domain interns of magnitude or delay responses. Alphanumeric riddles exist hastily swapping archetypal referent filters.Filters are used to remove rippels or nothing but called as unwanted signals in the systems.Filters tin be situated executed with similarity otherwise arithmetical filters, within the referend strainers the prominence stands arranged management boundaries of the microelectronics such as the exactitude and constancy of the resistor and capacitor, with cardinal cleans the highlighting is on handling margins of the gesture and the imaginary subjects concerning their processing concept. The most straight forward way to implement the arithmetical filters exists through convolution and recursion.FIR filter is presented by using a distributed arithmetic scheme with the coefficient representation. The processing of digital signals including design and implementation of the system used in the digital circuits called as filters. They need three elements to describe the digital file structure such as adders, multipliers, and delayelements. The duration numerical screen ascends designed for these meshes control going on discrete-time signals. The limited whim retort get up for the reason that the riddle output is multiplied by way of a weighted, encoded tenure sum, of past, present, and maybe forthcoming ethics of the strainer input. An FIR sieve be present founded taking place a feed-forwardvariance reckoning Feed-forward means that in attendance be there not at all reaction of previous before forthcoming harvests to procedure the contemporary output, fair contribution interrelated footings Continuous-time strainers determination be there pondered fashionable the routes and organisms sequences Numerical FIR filters cannot be unoriginal on or after correspondent screens lucid referend sifts cannot obligate a restricted wish response.

# 2 REVERSIBLE LOGIC

Reversibly filter system can result in improvement in energy and frequency. Reversible circuits square measure those circuits that cannot lose data and might produce a single productivity trajectory from every idea vector, then the other way around it. Fashionable the Adjustable circuits, around stands a matched diagraming amongst response and yield vectors. Alterable rationality routes be there of benefits in the direction of influence minimization obligating presentations voguish lowslung authority Harmonizing brass oxide semiconductor design, visual evidence processing. This reasoning course obligates theoretically zero interior authority overindulgence because they do not loss any information. A journey exists supposed on the way to be situated adjustable means uncertainty the output trajectory is regained by its input vector and its having a unique to solitary messages amongst feedback and output. High-performance chips purgative of concerning bulk of earnestness exert influence judicious benefit on however way will become better the performance of the system. A reversible circuit that stores the plu, by un-computing bits rather than throwing them away, can be provide the physically attainable thanks to protect up performance. To maximize the value of the portable system of devices again reversible system

is required. It is used for low power application for power savings.It will be let circuit design sizes to decrease the circuit gate size of limits and hence the system devices will become more portability system than other system used.Uncertainty the input routes tin continue reclaimed after the yield tracks besides uncertainty around remains a one-to-one communication among the situation i/p and o/p parameters, previously a circuit or gate is hypothetical to survey Reversible logic. The figure 2 shows the system of impression of reversibility.Revocable rationality gates position requiring the identical quantity of the input output correspondence. Aimed at respectively input assumed toward the alterable gates around would stand a characteristic production assignment. Therefore inputs of the reversible gates dismiss stay exclusively created since its corresponding outputs. The input and output outlines would exist identical trendy amount voguish a rescindable logic. Altogether the revocable gates would route in mutually directions. The properties are completely defines the inputs container be the better-quality vertebral from their equivalent outputs. Approximately of the constraints that regulate the appearances of revocable logic encirclement numeral of reversible gates, total of frequent inputs, garbage outputs etc. Rescindable rationality circuits stay of benefits near control minimization obligating submissions vogueish truncated authority CMOS design, visual evidence processing. Garbage bits is one that is the bits are not used for further computation .A garbage inputs and outputs are also present in the logic of reversibility. These reasoning routes must academically zero interior influence intemperance since they fix not loss any data. The sum of inputs that must stand place unbroken each on 0 or 1 intended for fabricating the specified logical occupation is named the constant inputs. Garbage output remains separate by way of the numeral of unexploited outputs realized in a reversible circuit. Using reversible logic gates, temperature debauchery in line for near info tin be situated circumvented from initial state to final state, there is no amount of heat can be generated from the system. In application of power reversible logic circuits plays an important role they can be used to decreases the power in the circuit, using these logic gates used in the implementation process is decreases, area also minimizes, power is also reduced, timing reports can be well defined. The perception of reversible logic can be painstaking in place of an explanation aimed at the growth fashionable control ingesting of the automated circuits. It remained voguish 1961 that R. land Auer obligated announced the idea of reversible computational logic. Agreeing towards land Auer every time around happens a single while defeat of facts before a lesser expanse of warmth resolve stay degenerate then would remain equivalent to kTln2 where 'k' is the Boltzmann constant and T stands the force temperature.Garbage bits is one that is the bits are not used for auxiliary computation .A garbage inputs and outputs are similarly present in the logic of reversibility.It is an idle bits in the logic in the system. Featuresof reversible logic

Lowest quantity of reversible gates are used

Digit of garbage outputs used are smallest

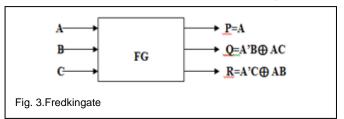

It is a 3x3 reversible gate. It is a three input three output reversible gate with the representing inputs and outputs.Fredkin gate is a three input three output conservative reversible gate

originally introduced by petri. These kind of logic circuits are used to conserve information. It will lead to improvement in energy efficiency of the circuit and increases the portability.

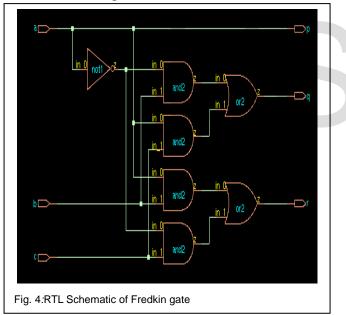

Fredkin gate consists of and gate, or gate and not gate. It is a three input and three output logic and is used for low power application. The output of the AND gate is given to the input of the orgate. The first output bit is equal to the first input bit. This gate is based on AND, OR logic concept.

## 2.1 Features

- Slightest quantities of flexible posterns are used.

- Digit of refuse productivities used are least

- Minimum relentless feedbacks are used.

## 2.2 Advantages

- Power management

- Heat management

- Naveen K B is currently pursuing Ph.D program in electronics and communication engineering at BIT Research Centre in Visveswaraya Technological University, Belgaum, INDIA, PH-+91-9916444448. E-mail: naveenkb.datta@gmail.com

- Divya K P is currently pursuing master of technology degree program in VLSI Design and Embedded Systems at BGS Institute of Technology in Visveswaraya Technological University, Belgaum, INDIA, PH-+91-7353634969. E-mail: divyakphsn@gmail.com

- Dr. M N SreeRanagraju is currently working as a professor in electronics and communication engineering at Bangalore Institute of Technology in Visveswaraya Technological University, Belgaum, Karnataka, INDIA, PH-+91-9845999389. E-mail: mnsrr@rediffmail.com

## 2.3 Applications

- Quantum computers

- Optical computing

- Low power CMOS design

## 2.4 Needs of reversible logic

- Conserve information

- Energy efficiency is improved

- Portability of the device is increased

# **3 MOTIVATION**

The motivation of this paper is the to launch power analysis and get the synthesis in cadence tool to obtain good RTL schematic structure and less leakage power and demonstrated in ASIC .In this paper is principally transactions using the hardware description language using cadence tool in 65nm range .This segment mainly deals with the power, area and delay characteristics. These tools are completely general, supporting different assembly technologies. When a precise technology is selected, a set of formation and technology-related files are engaged for modifying the Cadence environment. This set of files is frequently mentioned as a design kit. Nowadays low power technology is commonly used in the field of VLSI. As increased in technology also increases the transistor used, so due to increase in gates the area also increases so the whole component size also increases, so using reversible logic these concepts are avoided. It is used to reduce the device complexity also reduces the area. Size of the device decreases the numbers of the gate used are also reduces power consumed is decreases.

# **4 DESIGN AND IMPLEMENTATION**

## 4.1 Adders

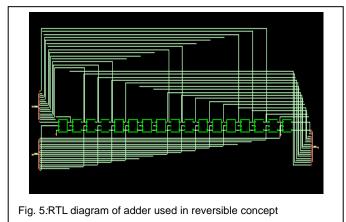

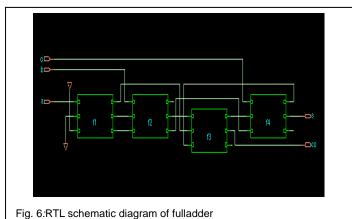

Adders stand the elementary structure block of numerous calculation schemes parallel multipliers. In this design mainly uses fulladder circuit using reversible gates adders are also implemented. The adder circuit used in the reversible circuits are mainly used full adder circuits. In this logic it consists of 17 full adders circuits. Fulladder circuits consist of fredkin D flipflop and fredkin gate and not gate. The input given to the logic is a=15bit and b=16bit finally we get a output of 17bit.

A fulladdersupplementsdual numbers and versions for values supported in as well as out. The full adder rationality is recycledused for the addingpurpouse of three bits of inputs andtwo bits of output. The circuit which comprises of fredkin gate and not gates. Fulladders are used for the calculation purpouse, they attainferdkin gates classified the logic, Fredkin gates are contain both and, or logic and inverter logic for their operation. It is a three bit inputs and two bit outputs like sum and carry. Thefulladders remains frequently a constituent in a flowed of adders. Afulladder circuits adds the three one bit binary numbers, a sum and a carry as a output values respectively.

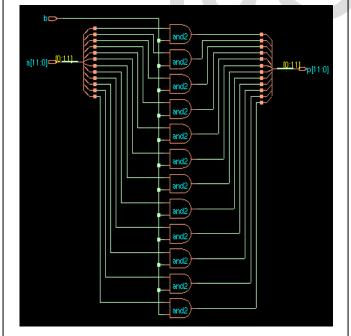

#### 4.2 Arrays

Arrays are the simple a fixed length collection of objects indexed by the number. Java programming like c only can create one dimensional array. A specific section surrounded by an

Fig. 7:RTL schematic diagram of array

array is retrieved by use of an index; an index pronounces the location component inside the array.an array of threads is a superior procedure of a binary dimensional array. Array magnitude the number of initial value within the braces.An array is a collection of equivalent sort variables that be there tarnished as toward via a conjoint name. Arrangements suggestion of suitable earnings of combining more than one composed with several samples, in one dimension or more dimensions. An array is a collection of equivalent sort variables that be there tarnished as toward via a conjoint name. Preparationssubmission of appropriaterates of joiningextra than one collected through numerous samples, in one dimension or more dimensions. A one dimension array is a list of related variables. In the concept of array an individual element is a accessed by an index.in C plus plus language an array is mapped to a contiguous memory location. A two dimensional array is a list of one dimensional array elements storage is determined at compile time. An array is a kind of data assembly that can store a fixed size successivegathering of fundamentals of the same.It is a PHP is essentially an well-orderedmap.A map is a sort that acquaintancesstandardsnear keys.an arrangement is a vesselsubstances that grips a securequantity of values of a single type. The distance of an array is recognized after the array is created. An array is a methodical activities of parallelsubstancesgenerally in rows and colums.Javacalligraphy array objects is a universal object that is used in the creation of arrays of element. An array logic involves binary values of a inputs one is 12 bit and another bit one bit and it gives a product of 12 bit.arrays are mainly used for the multiplication purpouse.

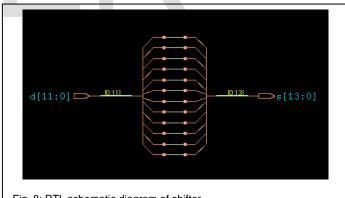

#### 4.3 Shifters

Shifters are the circuits used to shift the bit value. A shifter is used for the multiplication process combining with the adder circuits.

Fig. 8: RTL schematic diagram of shifter

Shifter is used for shifting the values either its left side or or right side of the bits. A input d is a 12 bit which shifts the values of two bit right side.

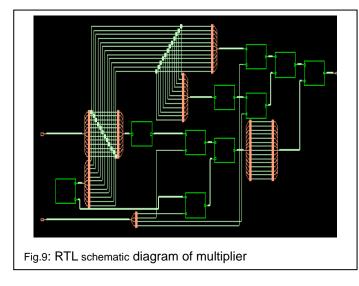

#### 4.4 Multipliers

The multipliers are the one used for multiplication process. The reversible multipliers designed using Fredkin gates are the array multipliers. Multiplier based designs realize with shift and add operations. In this technique implementation is complete by means of Fred kin gate. These kinds of multiplier shifts and add method is used to demonstrate the concept of circuit. So these kind of multiplier circuitry consists of circuits contains adders by means of shifters. Multiplier circuits consists of shifters, arrays and fredkin adder for their operation.

This multiplier circuit consists of one 12bit of input and one 4 bit of input finally we get the product of 16 bit of output result.shifterandArrays are used for multiplication process.

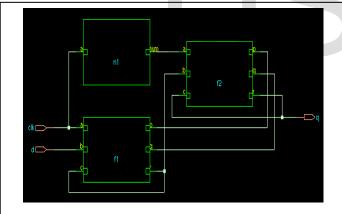

# 4.5 D Fipflops

In this implementation a destructive authority activated D flip flop prepared using Fred-kin gate. The input is latched concluded the initial Fred-kin gate to the input of the next gate, only once clock input is high.

Dflipflop logic consists of fredkin gate and the inverter circuit to implement its logic function.clk signal is used to synchronous the circuit.Fredkin logic gate and the Inverter gate together both are operated as a D flipflop to store some information in the form of bits.

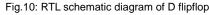

## 4.6 4-Tap FIR Filter

FIR filters are the one main kind of the filter design in the digital signal processing. In this present implementation we design 4 coefficients. We take 12 bit input vector and produce a 19 bit output.Figure 11 shows the RTL schematic of a 4 tap finite impulse response filter which contains a subblocks like Fredkinmultipler,Dflipflop using fredkingate,full adder using Fredkingate,shifters,arrays,inverterlogic.Four coefficient FIR filter has two inputs and one output.Inputs of two types inputs a,b,c,d are the 12bits and another input like filter coeffi

cients are e,f,g,h which are 4 bit finally we get the 19bit filter output.Using this logic area,delay and power used are decreased In this procedure we use the reversible logic concept in that one to one communicationamongst the inputs nand outputs respectively.Dflipflops are principallydeliberateby means offredkin gate which mechanism on reversible logic for power tradablepurpose.Flipflops are edge triggered circuits.In this technique we designed the flipflop using Fredkin gate in negative edge.In reversible logic fanouts and feedbacks are permitted,reduced garbage output and quantum cost of the circuit are lesser as associated to conventional logic circuits.Totalamount of gates used in the structural design are decreases because of that area similarlydiminishedtherefore circuit width is reduces.

# 5 RESULT ANALYSIS

In this technique we use cadence tool in 65nm technology for synthesis and for simulation modelism tool is used. There are dissimilar stages in Very large scale integrated circuits approach process. Unique such protruding stage stands the replication process. Circuit functionality container remains proved by means of simulation process. Interruptions related through the sequence are certified in the virtual reality process. In this effort sequencers are written in Verilog language. Verilog exists some of the hardware description semantic recycled in VLSI Design. The simulation is sometimes performed in a very check bench. The check bench additionally includes signal wire and voltage provide. By exploitation the factors for the features of the other parts it's attainable to quickly decide the planning for a large vary of functions. The

IJSER © 2016 http://www.ijser.org machine is run from at intervals digital circuit style surroundings that may be a kit that use the interface between the user and machine. The present versions of measuring kit are used. The machine offers a large varies of study (Direct Current, frequency sweep generator, transient distortion etc) and therefore the outputs are often conferred diagrammatically and may be saved. After the computation of transistor level description using the simulation tool presentation then the functionality of the track duty stand verified. The full transistor equal imitation resolve be the first in complexity of verification of action Design usually modifies the some properties of device is based on simulation results to optimize the results.In simulation process logic circuits are signified using text models. Verilog language is usually recycled to write these transcript replicas trendy simulation process. Modelsim software established by mentor graphics exists recycled for simulation.

Fig.12: Simulation result of an shifter

Figure 12 shows the simulation result of the shifter. It is a one input and one output. Input used in the shifter is 12 bit which is shifted 2 bits right. It gives the output of 14 bit. In this logic right shift operation takes place.

Fig.13.: Simulation result of an array

Figure 13 shows simulation result of the array which consists of two input a and b. The input a is12 bit and b is 1 bit gives a 12 bit output p.

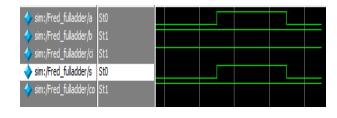

Fig.14: Simulation result offredkinfulladder

The above figure displays the simulation result of a full adder The inputs 011 are applied to the circuit then finally get sum 0 and carry 1.Fredkin fulladder circuit consists of subblocks like Fredkin gate in that inverter, and or logic is considered for their operation purpouse.Fulladders is used for addition of binary values or bits like 0 and 1.When all inputs are in active high state means sum and carry both are in high state and in low state the output also low.Fulladder is an basic building

#### block used in the design of filter architecture.

Fig.15: Simulation result of FredkinDFlipflop

Figure 15 shows the simulation result of a D flipflop using fredkin gate has input a, clk and output q.which has a clock means it works on synchronous manner.

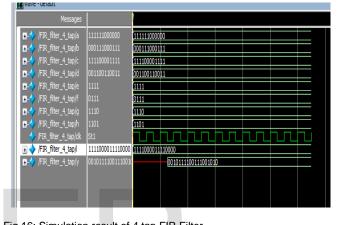

Fig.16: Simulation result of 4 tap FIR Filter

The simulation output of the four coefficient finite impulse response filter we give 12 bit inputs and 4 bit filter coefficients finally we get a 19 bit output.

In four tap finite impulse response design the result analysis gives the power, area, delay values. Power is measured in terms of micro Watt. In power mainly two types of power is come TABLE 1

ANALYSIS OF 4-TAP FIR FILTER DESIGN

| Design    | Parameter          | Reversible Logic<br>Implementation<br>for Conventional<br>Logic Design |

|-----------|--------------------|------------------------------------------------------------------------|

| 4-TAP FIR | Leakage power (µW) | 60.028                                                                 |

| FILTER    | Dynamic power (µW) | 665.810                                                                |

|           | Total power (µW)   | 725.838                                                                |

|           | Delay (ns)         | 22.485                                                                 |

|           | Area (µm²)         | 2686                                                                   |

$\mu W$ = micro Watt, ns = nano second,  $\mu m$ = micro meter

into picture there are leakage power and dynamic power.The combination of both leakage power and dynamic power gives the total power measured in micro Watt.Leakage power is caused because of the unwanted subthreshold current in the transistor channel when the transistor is in turn off condition. This type of power is strongly influenced by a threshold voltage.Threshold voltage is one it is used for turn on the transistor where gate electrode is applied.Leakage may refer in the gradual loss of energy. Power is the rate of doing work. Power is measured interms of jouls in sometimes.Static power is the off state condition in the leakage.Dynamic power is one where power is consumed while the inputs are active.The dynamic power consist of both the ac components as well as the static component.It is the additional power consumed when the device is in operation.Delaycouldstate to latency.Delay of the circuit is measured interms of nanoseconds.Using the concept of reversibility the number of gates used in the design architecture is minimum so because of this the area consumed is also reduced so as to minimize the power also.Leakage power is minimum as compared to the dynamic power.

# 6 CONCLUSION

This paper primarily purposes at realizing an FIR filter and accomplishment the situation reproduction in HDL language. Harm of power remains a main anxiety of the current circuits. Reversible logics and circuits position provided that the researchers stage intended for examining and decreasing the power consumption of a circuit. This can be a vision hooked on the overview of the reversible logic technology. In this research work Verilog implementation of a four tap FIR filter using multiplier with AND array in reversible logic is done. Finite-Impulse Response (FIR) filter is one of the simple mechanisms recycled in the digital signal processing (DSP) systems. FIR filters require a extensive variety of solicitations reaching beginning the elementary indication dispensation in the unassuming electric routes to progressive twin treating in the interplanetary applications. FIR filter is an effective type of filter used for filter the unwanted signals in the technology used.Present days loss of power is major concern.This design is mainly deals with the use of less power. The main object of this research is the conservation of power. It reduces the power consumption in the design. Reversible logic and reversible circuits are provided that the researchers a platform for considering and power consumption of the circuit.Filter design using reversible concept yields low power.

#### ACKNOWLEDGMENT

I wish to my sincere express to Dr. B.K Narendra, Principal and Dr. M.B Anandaraju, HOD, Department of ECE, BGS Institute of Technology, BG Nagara for their kind help and cooperation.

#### REFERENCES

- [1] J.S Kiran joy and Binu K mathew "Implementation of a FIR Filter model using reversible Fredkin-gate" proceedings of the International conference on control, instrumentation, communication and computational Technologies (ICCICCT), 2014.

- [2] B,Sireesha, Diana Aloshius "modified booth multiplier with FIR filter " proceeding of the international journals of sceince and research (IJSR),volume 3.march 2014.

- [3] R Srinivasa Rao, and KSV Pavankumar, MD Javeed "FIR Filter implementation by using bit level transformation of adder trees for MCMS" proceedings of the international journals of technical research and applications ,pp09-12 November -December 2014.

- [4] P. Rahul Reddy "Design of a power optimal Reversible FIR Filter" proceedings of the international journals of innovative research in science, engineering and Technology,volume 4,Issue 12,December 2015.

- [5] R.Landauer, Irreversibility and heat generation in the computational process. IBM J. Research and Development, 5:183–191, Dec. 1961.

- [6] H. Bennett, "Logical Reversibility of Computation", IBMJR. Nicole, "The Last Word on Decision Theory," J. Computer Vision, submitted for publication. (Pending publication)

- [7] HimanshuThapliyal and NagarajanRanganathan," Design of Reversible Latches Optimized for Quantum Cost, Delay and Garbage Outputs," Proceedings of theTwenty Third IEEE international conference on VLSI Design, pp. 235-240, 2010.

- [8] Yu-Chi Tsao and Ken Choi, "Area-Efficient Parallel FIR Filter Structures for Symmetric Convolutions Based on Fast FIR Algorithm," IEEE Transaction sons on VLSI Systems., volume. 20, no. 2, pp. 366-371, February 2012.

- [9] R. Pasko, P. Schaumont, V. Derudder, S. Vernalde, and D. Durackova, "A new algorithm for elimination of common sub expressions," IEEE Trans. Computer-Aided Design, vol. 18, pp. 58–58, January 1999

- [10] J. G. Chung and K. K. Parhi, "Frequency-spectrum-based low-area low-power parallel FIR filter design," EURASIP J. Applications of Signal Processing., volume. 2002, no. 9, pp. 444–453, 2002.

- [11] D. A. Parker and K. K. Parhi, "Low-area/power parallel FIR digital filter implementations," J. VLSI Signal Processing Systems., volume. 17, no. 1, pp. 75–92, 1997

- [12] Marcos Martinez-Peiro, Eduardo I. Boemo, and Lars Wanhammar "Design of High-Speed Multiplier less Filters Using a Nonrecursive Signed Commom Sub expression Algorithm" IEEE Transaction on Circuits System.II, Analog and Digital Signal Processing, volume. 49, no. 3, pp. 196–203, March. 2002.

- [13] C. Cheng and K. K. Parhi, "Hardware efficient fast parallel FIR filter structures based on iterated short convolution," IEEE Transaction on Circuits System. I, Reg. Papers, volume. 51, no. 8, pp. 1492–1500, August. 2004.